Home > SiSoft > QSI > QSI Design Kits

QSI Design Kits

Quantum-SI 설계 키트에 대한 시간과 비용 슬래시(Slash) 분석

SiSoft는 Quantum-SI에 대한 설계 분석 키트들을 만들어내기 위해 반도체 회사들 및 고객들과 직접 협력합니다.

Quantum-SI 설계 키트는 인터페이스 설정이 신호 무결성과 타이밍 효과들에 대해 완전히 분석될 수 있도록 합니다. 각 키트는 사전에 수정되고, 통합된 타이밍과 시간 무결성

모델들, 다양한 각 네트 클래스/전송 네트에 대한 위상, 상세한 문서를 포함합니다. 이러한 키트는 즉시 실행할 준비를 갖춘, 사전 설정된 분석 환경을 제공함으로써 수개월의

전통적 분석 주기를 몇 주로 단축할 수 있습니다.

Quantum-SI Architectural Design Kits(구조적 설계 키트)

이 키트는 범용 타이밍과 신호 무결성 모델들을 포함합니다. 장치 타이밍은 산업 표준 규격이나 인터페이스 클래스에 대한 일반적 예산을 기준으로 합니다.

신호 무결성 모델들은 Quantum-SI의 기술 모델 라이브러리의 대표적인 패키지 기생요소들(parasitic)과 버퍼 모델들을 기반으로 합니다. 구조적 키트는 특정 구성요소들이

선택되지 않고, 장치 타이밍과 신호 무결성 목표들이 시스템 수준의 분석을 기반으로 정의되어야 하는 시기인, 설계 주기의 초기 단계들에서 유용합니다. 또한 구조적 설계 키트는

더 상세한 설계 키트들을 개발하기 위한 템플릿으로 기능합니다. 즉, 범용 모델들은 설계 프로세스들인 특정 요소(component) 모델들에 의해 교체될 수 있습니다.

Quantum-SI Implementation Kits(실행 키트)

이 키트는 특정 요소 결합들을 위한 타이밍과 신호 무결성 모델들을 포함합니다. 요소 데이터시트 타이밍 규격은 특정 로딩과 측정 조건들을 기반으로 합니다.

즉, 신호 무결성이 지연 시뮬레이션들과 어떻게 연결되는지 구동하기 위한, 이러한 규격의 세부사항들이 수행되고, 측정되어야 합니다. 각 Quantum-SI 실행 키트에서, SiSoft의

전문가들은 장치 데이터시트에서 관련된 장치 타이밍 parameter들을 추출하고, pin-특화 장치 타이밍 모델을 생성했으며, 부합하는 신호 무결성 장치 모델이 정확한 기준 로드, measurement thresholds(측정 임계치)와 입력slew rate(회전율)derating데이터 를 포함하도록 보장했습니다.

Quantum-SI실행 키트들은 사용자들이 설계 특화 데이터를 입력하고, 즉시 시뮬레이션을 시작할 수 있도록 하는 완벽한 pin 특화 분석 설정입니다.

이러한 키트들의 장치 모델들은 Pin에 특화되어 있기 때문에, 실행 키트들은 또한 사용자의 설계 데이터베이스의 포스트 레이아웃 분석에 사용될 수 있습니다.

Quantum-SI 검증 키트(Validation Kits)

이 키트는 특정 PCB 설계에 대한 완벽한 프리와 포스트 라우트 분석 환경을 제공하며 실행 키트들에 기반을 두고 있습니다. 이러한 키트들은 양성(positive) 설계 마진들로 입증된

속도들에서 장치 운영들에 대한 증명으로 반도체 벤더들에 의해 제공될 수 있습니다. 검증 키트는 벤더의 기준 보드 설계에 대한 데이터를 포함할 수 있으며, 고객들이 기준 보드를

사례로 사용하여 장치를 “디자인 인(design-in-협의 생산)” 할 수 있도록 합니다. 사용자들이 자신들의 고유 환경을 위해 라우팅 길이(routing lengths)를 조정함에 따라,

Quantum-SI는 사용자의 설계를 위한 설계 마진들을 제공하며, 신호 무결성과 타이밍 분석을 수행합니다. 사용자들은 자체 PCB 데이터를 가지고 검증 키트에서 기준 보드 데이터를

쉽게 교체할 수 있으며, 포스트 라우트 분석을 위해 키트를 직접 이용할 수 있습니다.

진보된 키트 역량들

Quantum-SI 설계 키트들은 반복적인 분석 업무들을 자동화하기 위해 Quantum-SI의 강력한 역량들을 이용합니다. SI 분석과 타이밍 분석이 어떻게 수행되는지 구동하기 위해

이러한 정보를 사용하는 Quantum-SI를 통해, 인터페이스가 어떻게 모델로 구축되고, 분석되어야 하는지에 대한 중요한 측면들을 설계 키트들에서 얻을 수 있습니다:

Reflections(반사)들을 최소화하기 위해 on-die termination을 사용하는 기술들은 다양한 장치 작용들(구동 대 수신, 종단(terminating) 대비 종단(non terminating), 다양한 터미네이션 값)을 보여주는 다수의 시뮬레이션 모델들을 필요로 합니다. 이것은 다수의 I/O 버퍼 모델들(IBIS 모델들에 대해

일반적인)을 사용함으로써, 혹은 다수의 제어 상태들(트랜지스터 수준의 SPICE 모델들에 일반적인)을 가진 단일 I/O 버퍼 모델의 사용을 통해 제공될

수 있습니다. 개별 시뮬레이션을 위해 사용되는 모델들은 시뮬레이션 되는 버스 트랜잭션(bus transaction)에 따라(즉, 구동되는 장치, 그리고 수신되는

장치에 따라) 달라질 수 있습니다. Quantum-SI 설계 키트들은 시뮬레이션 동안 시뮬레이션 모델 할당들의 자동 관리를 가능하게 하면서, 다양한

각 데이터 트랜잭션을 시뮬레이션 하기 위해 사용되는 모델 설정을 구현합니다.

DDR2/DDR3 같은 고속 기술들은 100ps 혹은 그 이하의 타이밍 마진들을 가질 수 있으며, 이 경우 SI와 타이밍 분석의 정확한 통합이 중요합니다.

이러한 기술들은 장치의 입력 핀에서 신호의 slew rate를 바탕으로 하여 장치의 특정 setup(설정)과 hold(보류) 시간 요건들을 변경합니다.

Quantum-SI는 input slew rate 측정과 이에 부합하는 장치 타이밍 예산 조정을 자동화 합니다. Slew rate derating data는사용자의 관점에서 전체

프로세스를 자동화하는Quantum-SI 설계 키트들로 공급되는장치 모델들에 포함됩니다. 슬루 율과 이에 부합하는 타이밍 예산들에 대한 영향이

측정되는 분석 세부사항들은Quantum-SI에 의해 생성되는 분석 보고서들에 기록됩니다.

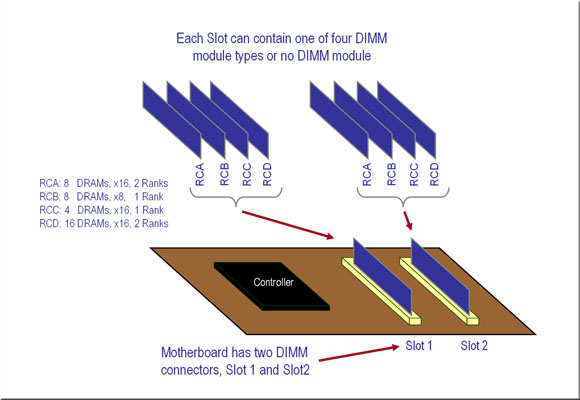

PCB 설계는 종종 다수의 여러 플러그 인 메모리 구성들과 다수의 메모리 벤더들과의 협력이 요구됩니다. 사용되는 메모리 모듈의 형태와 연결되는

슬롯에 따라, 로딩(그리고 이에 따른 신호 품질)이 상당히 변할 수 있습니다. 설계에 대한 각 변화는 모든 가능한 개체군들에 걸쳐 분석되어야 하기

때문에, 여러 메모리 개체단들을 자동으로 분석할 수 있는 것이 중요합니다.

Quantum-SI 설계 키트들은 툴이 자동으로 분석하는, 사전 정의된 메모리 개체군들을 포함할 수 있습니다. 설계 키트의 개체군들은 기존 경우들을

재설정하거나, 새로운 경우들을 추가하기 위해 사용자에 의해 손쉽게 변경될 수 있습니다.

샘플DDR2 SoDIMM Kit

Quantum-SI는 1과 2 슬롯 SoDIMM모듈에 대한JEDEC 설정으로 DDR2 분석을 지원하는 샘플 실행 설계 키트를 함께 제공합니다.

이 프리 레이아웃 분석 환경은 다음을 포함합니다.

• JEDEC raw cards A, B, C와 D를 이용하는 각 1 슬롯과 2 슬롯 SoDIMM 설정에 대한 매개변수화 위상

• 네트 클래스(전송 네트)

• SiSoft parts

• Micron Technology, Inc("Micron")의DDR2SDRAM 메모리 장치들에 대한 IBIS와 타이밍 모델들

• 범용 메모리 제어장치에대한 IBIS와 타이밍 모델들

샘플 키트는 사용을 위한 준비가 되어 있으며, 고객의 특정 요건들을 충족시키기 위해 쉽게 재설정될 수 있습니다. 이것은 신호 무결성과 타이밍 분석들이 광범위한 기생 변수들의

프로세스, 전압, 온도 조건들에 대해 빠르게 수행될 수 있도록 합니다. 이 외에, on-die termination(ODT)과 slew rate derating이 자동으로 수행되며, 모든 DDR2 파형 프로세싱

레벨들이 지원됩니다.

• DDR2 SoDIMM 키트 문서 보기

• Micron Technology, Inc에 대한 더 많은 정보

더 많은 정보를 위해, sales@sisoft.com.에 문의하십시오.